Uban sa kasamtangan nga padayon nga pag-uswag sa mga de-koryenteng mga sakyanan, nagkadaghang mga teknisyan ug tiggamit ang naghatag ug dugang nga pagtagad sa taas nga boltahe nga kaluwasan sa mga de-koryenteng sakyanan, ilabi na karon nga ang mas taas nga mga boltahe sa plataporma (800V pataas) padayon nga gipadapat. Isip usa sa mga lakang aron maseguro ang taas nga boltahe nga kaluwasan sa mga de-koryenteng sakyanan, ang taas nga boltahe nga interlock (HVIL) nga pag-andar labi nga gipasiugda, ug ang kalig-on ug katulin sa pagtubag sa function sa HVIL padayon nga gipauswag.

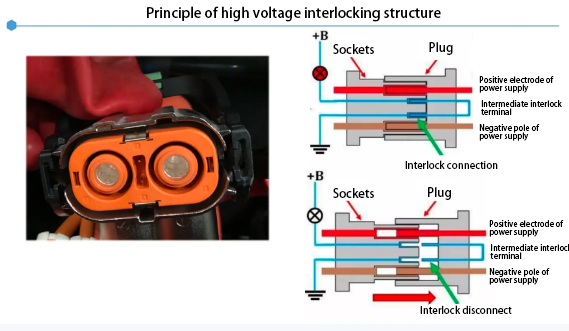

Taas nga Boltahe nga Interlock(HVIL alang sa mubo), mao ang usa ka luwas nga disenyo nga pamaagi sa pagdumala sa taas nga boltahe circuits uban sa ubos nga boltahe signal. Sa disenyo sa taas nga boltahe nga sistema, aron malikayan ang arko nga gipahinabo sa taas nga boltahe nga konektor sa aktwal nga operasyon sa proseso sa pagdiskonekta sa kuryente, ug pagsira, ang usa ka taas nga boltahe nga konektor sa kasagaran adunay usa ka "taas nga boltahe nga interlock" gimbuhaton.

Ang usa ka taas nga boltahe nga sistema sa koneksyon nga adunay taas nga boltahe nga interlocking function, gahum, ug interlocking nga mga terminal kinahanglan nga makab-ot ang mosunod nga mga kondisyon kung magkonektar ug magdiskonekta:

Kung konektado ang taas nga boltahe nga sistema sa koneksyon, ang mga terminal sa kuryente konektado una ug ang mga interlocking terminal konektado sa ulahi; sa diha nga ang taas nga boltahe nga sistema sa koneksyon madiskonekta, ang mga interlocking terminal madiskonekta una ug ang mga power terminal maputol sa ulahi. Sa ato pa:ang taas nga boltahe nga mga terminal mas taas kaysa sa ubos nga boltahe nga interlock nga mga terminal, nga nagsiguro sa pagka-epektibo sa taas nga boltahe nga interlock signal detection.

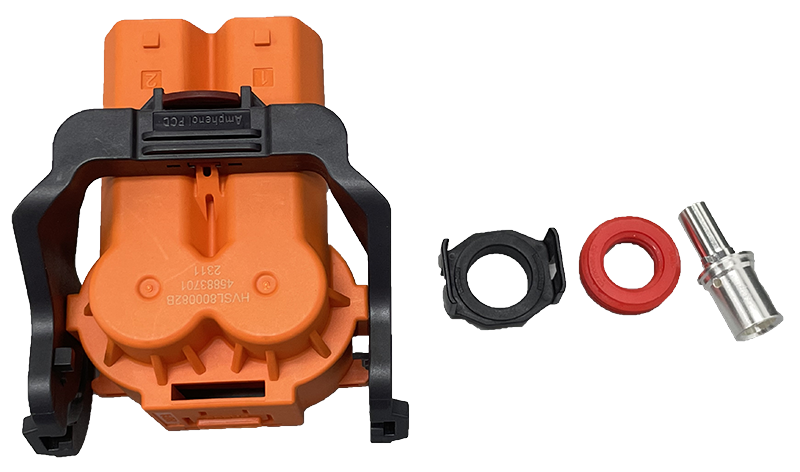

Ang mga high-voltage interlocks kasagarang gigamit sa high-voltage electrical circuits, sama sa high-voltage connectors, MSDs, high-voltage distribution box, ug uban pang mga sirkito. Ang mga konektor nga adunay taas nga boltahe nga mga interlock mahimong ma-disconnect pinaagi sa logic timing sa taas nga boltahe nga interlock kung ang pag-unlock gihimo sa ilawom sa gahum, ug ang oras sa pagdiskonekta adunay kalabotan sa gidak-on sa kalainan tali sa epektibo nga mga gitas-on sa kontak sa taas nga boltahe nga interlock. mga terminal ug ang mga terminal sa kuryente ug ang katulin sa pagdiskonekta. Kasagaran, ang oras sa pagtubag sa sistema sa interlocking terminal circuit naa sa taliwala sa 10 ~ ug 100ms kung ang oras sa pagbulag sa sistema sa koneksyon (unplugging) mas gamay kaysa sa oras sa pagtubag sa sistema, adunay peligro sa kaluwasan sa elektrisidad nga pag-plug ug pag-unplug, ug ang Ang ikaduha nga pag-abli gidisenyo aron masulbad ang problema sa kini nga oras sa pagdiskonekta, kasagaran, ang ikaduha nga pag-abli epektibo nga makontrol kini nga oras sa pagdiskonekta nga labaw pa sa 1s, aron masiguro ang kaluwasan sa operasyon.

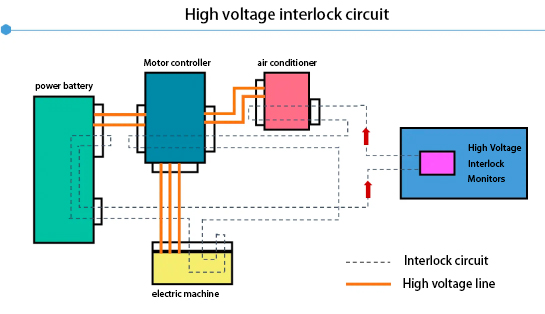

Ang pag-isyu, pagdawat, ug determinasyon sa interlock signal tanan natuman pinaagi sa manager sa baterya (o VCU). Kung adunay usa ka taas nga boltahe nga interlock nga sayup, ang awto dili tugutan nga moadto sa taas nga boltahe nga gahum, ug ang mga interlock nga sirkito sa lainlaing mga modelo sa awto adunay piho nga mga kalainan (lakip ang mga kalainan sa mga interlock nga pin ug taas nga boltahe nga mga bahin nga gilakip sa interlock ).

Ang numero sa ibabaw nagpakita sa usa ka hardwired interlock, gamit ang usa ka hardwire aron makonektar ang feedback signal gikan sa matag high-voltage component connector sa serye aron maporma ang usa ka interlock circuit, kung ang usa ka high-voltage nga component sa circuit mapakyas sa interlock, ang interlock monitoring device diha-diha dayon. i-report sa VCU, nga magpatuman sa katugbang nga estratehiya sa pagpaubos sa kuryente. Bisan pa, kinahanglan nga matikdan nga dili nato tugutan ang usa ka high-speed nga sakyanan nga kalit nga mawad-an og gahum, mao nga ang gikusgon sa sakyanan kinahanglan nga tagdon sa pagpatuman sa power-down nga estratehiya, mao nga ang mga hard-wired interlocks kinahanglan nga gigrado kung ang estratehiya giporma.

Pananglitan, ang BMS, RESS (sistema sa baterya), ug OBC giklasipikar isip level 1, MCU ug MOTOR (electric motor) isip level 2, ug EACP (electric air conditioning compressor), PTC, ug DC/DC isip level 3.

Nagkalainlain nga mga estratehiya sa HVIL ang gisagop para sa lain-laing lebel sa interlocking.

Tungod kay ang taas nga boltahe nga mga sangkap gipang-apod-apod sa tibuuk nga salakyanan, kini nagdala sa usa ka taas nga interlock nga hardwire nga gitas-on, nga miresulta sa komplikado nga mga kable ug pagtaas sa gasto sa mga low-voltage nga mga wiring harness. Bisan pa, ang hardwire interlocking nga pamaagi kay flexible sa disenyo, simple sa logic, intuitive kaayo, ug makatabang sa kalamboan.

Oras sa pag-post: Ene-26-2024