ਇਲੈਕਟ੍ਰਿਕ ਵਾਹਨਾਂ ਦੇ ਮੌਜੂਦਾ ਨਿਰੰਤਰ ਵਿਕਾਸ ਦੇ ਨਾਲ, ਵੱਧ ਤੋਂ ਵੱਧ ਟੈਕਨੀਸ਼ੀਅਨ ਅਤੇ ਉਪਭੋਗਤਾ ਇਲੈਕਟ੍ਰਿਕ ਵਾਹਨਾਂ ਦੀ ਉੱਚ-ਵੋਲਟੇਜ ਸੁਰੱਖਿਆ ਵੱਲ ਵੱਧ ਤੋਂ ਵੱਧ ਧਿਆਨ ਦੇ ਰਹੇ ਹਨ, ਖਾਸ ਤੌਰ 'ਤੇ ਹੁਣ ਜਦੋਂ ਉੱਚ ਪਲੇਟਫਾਰਮ ਵੋਲਟੇਜ (800V ਅਤੇ ਇਸ ਤੋਂ ਵੱਧ) ਲਗਾਤਾਰ ਲਾਗੂ ਹੁੰਦੇ ਹਨ। ਇਲੈਕਟ੍ਰਿਕ ਵਾਹਨਾਂ ਦੀ ਉੱਚ ਵੋਲਟੇਜ ਸੁਰੱਖਿਆ ਨੂੰ ਯਕੀਨੀ ਬਣਾਉਣ ਦੇ ਉਪਾਵਾਂ ਵਿੱਚੋਂ ਇੱਕ ਦੇ ਰੂਪ ਵਿੱਚ, ਉੱਚ ਵੋਲਟੇਜ ਇੰਟਰਲਾਕ (HVIL) ਫੰਕਸ਼ਨ ਉੱਤੇ ਜ਼ੋਰ ਦਿੱਤਾ ਗਿਆ ਹੈ, ਅਤੇ HVIL ਫੰਕਸ਼ਨ ਦੀ ਸਥਿਰਤਾ ਅਤੇ ਪ੍ਰਤੀਕਿਰਿਆ ਦੀ ਗਤੀ ਵਿੱਚ ਲਗਾਤਾਰ ਸੁਧਾਰ ਕੀਤਾ ਜਾ ਰਿਹਾ ਹੈ।

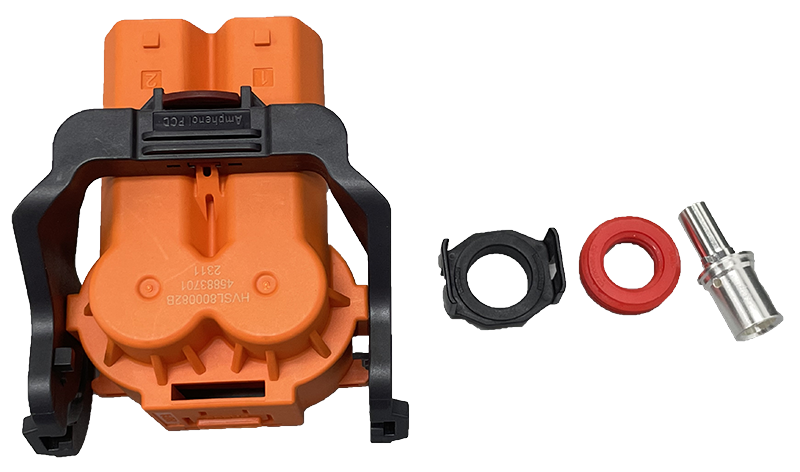

ਹਾਈ ਵੋਲਟੇਜ ਇੰਟਰਲਾਕ(ਛੋਟੇ ਲਈ HVIL), ਘੱਟ ਵੋਲਟੇਜ ਸਿਗਨਲਾਂ ਦੇ ਨਾਲ ਉੱਚ ਵੋਲਟੇਜ ਸਰਕਟਾਂ ਦਾ ਪ੍ਰਬੰਧਨ ਕਰਨ ਲਈ ਇੱਕ ਸੁਰੱਖਿਆ ਡਿਜ਼ਾਈਨ ਵਿਧੀ ਹੈ। ਹਾਈ-ਵੋਲਟੇਜ ਸਿਸਟਮ ਦੇ ਡਿਜ਼ਾਇਨ ਵਿੱਚ, ਇਲੈਕਟ੍ਰਿਕ ਡਿਸਕਨੈਕਟ ਕਰਨ ਅਤੇ ਬੰਦ ਕਰਨ ਦੀ ਪ੍ਰਕਿਰਿਆ ਦੇ ਅਸਲ ਸੰਚਾਲਨ ਵਿੱਚ ਉੱਚ-ਵੋਲਟੇਜ ਕਨੈਕਟਰ ਦੁਆਰਾ ਹੋਣ ਵਾਲੇ ਚਾਪ ਤੋਂ ਬਚਣ ਲਈ, ਇੱਕ ਉੱਚ-ਵੋਲਟੇਜ ਕਨੈਕਟਰ ਵਿੱਚ ਆਮ ਤੌਰ 'ਤੇ "ਹਾਈ-ਵੋਲਟੇਜ ਇੰਟਰਲਾਕ" ਹੋਣਾ ਚਾਹੀਦਾ ਹੈ। ਫੰਕਸ਼ਨ.

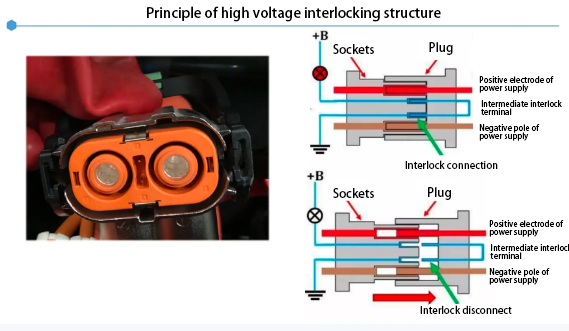

ਉੱਚ-ਵੋਲਟੇਜ ਇੰਟਰਲੌਕਿੰਗ ਫੰਕਸ਼ਨ, ਪਾਵਰ ਅਤੇ ਇੰਟਰਲੌਕਿੰਗ ਟਰਮੀਨਲਾਂ ਦੇ ਨਾਲ ਇੱਕ ਉੱਚ-ਵੋਲਟੇਜ ਕਨੈਕਸ਼ਨ ਸਿਸਟਮ ਨੂੰ ਕਨੈਕਟ ਅਤੇ ਡਿਸਕਨੈਕਟ ਕਰਨ ਵੇਲੇ ਹੇਠ ਲਿਖੀਆਂ ਸ਼ਰਤਾਂ ਨੂੰ ਪੂਰਾ ਕਰਨਾ ਚਾਹੀਦਾ ਹੈ:

ਜਦੋਂ ਹਾਈ-ਵੋਲਟੇਜ ਕੁਨੈਕਸ਼ਨ ਸਿਸਟਮ ਜੁੜਿਆ ਹੁੰਦਾ ਹੈ, ਪਾਵਰ ਟਰਮੀਨਲ ਪਹਿਲਾਂ ਜੁੜੇ ਹੁੰਦੇ ਹਨ ਅਤੇ ਇੰਟਰਲੌਕਿੰਗ ਟਰਮੀਨਲ ਬਾਅਦ ਵਿੱਚ ਜੁੜੇ ਹੁੰਦੇ ਹਨ; ਜਦੋਂ ਹਾਈ-ਵੋਲਟੇਜ ਕੁਨੈਕਸ਼ਨ ਸਿਸਟਮ ਨੂੰ ਡਿਸਕਨੈਕਟ ਕੀਤਾ ਜਾਂਦਾ ਹੈ, ਇੰਟਰਲਾਕਿੰਗ ਟਰਮੀਨਲ ਪਹਿਲਾਂ ਡਿਸਕਨੈਕਟ ਹੁੰਦੇ ਹਨ ਅਤੇ ਪਾਵਰ ਟਰਮੀਨਲ ਬਾਅਦ ਵਿੱਚ ਡਿਸਕਨੈਕਟ ਹੁੰਦੇ ਹਨ। ਇਹ ਕਹਿਣਾ ਹੈ:ਉੱਚ ਵੋਲਟੇਜ ਟਰਮੀਨਲ ਘੱਟ ਵੋਲਟੇਜ ਇੰਟਰਲਾਕ ਟਰਮੀਨਲਾਂ ਨਾਲੋਂ ਲੰਬੇ ਹੁੰਦੇ ਹਨ, ਜੋ ਉੱਚ ਵੋਲਟੇਜ ਇੰਟਰਲਾਕ ਸਿਗਨਲ ਖੋਜ ਦੀ ਪ੍ਰਭਾਵਸ਼ੀਲਤਾ ਨੂੰ ਯਕੀਨੀ ਬਣਾਉਂਦੇ ਹਨ।

ਹਾਈ-ਵੋਲਟੇਜ ਇੰਟਰਲਾਕ ਆਮ ਤੌਰ 'ਤੇ ਉੱਚ-ਵੋਲਟੇਜ ਇਲੈਕਟ੍ਰੀਕਲ ਸਰਕਟਾਂ, ਜਿਵੇਂ ਕਿ ਉੱਚ-ਵੋਲਟੇਜ ਕਨੈਕਟਰ, MSD, ਉੱਚ-ਵੋਲਟੇਜ ਵੰਡ ਬਕਸੇ, ਅਤੇ ਹੋਰ ਸਰਕਟਾਂ ਵਿੱਚ ਵਰਤੇ ਜਾਂਦੇ ਹਨ। ਉੱਚ-ਵੋਲਟੇਜ ਇੰਟਰਲਾਕ ਵਾਲੇ ਕਨੈਕਟਰਾਂ ਨੂੰ ਉੱਚ-ਵੋਲਟੇਜ ਇੰਟਰਲਾਕ ਦੇ ਤਰਕ ਸਮੇਂ ਦੁਆਰਾ ਡਿਸਕਨੈਕਟ ਕੀਤਾ ਜਾ ਸਕਦਾ ਹੈ ਜਦੋਂ ਅਨਲੌਕਿੰਗ ਪਾਵਰ ਦੇ ਅਧੀਨ ਕੀਤੀ ਜਾਂਦੀ ਹੈ, ਅਤੇ ਡਿਸਕਨੈਕਟ ਹੋਣ ਦਾ ਸਮਾਂ ਉੱਚ-ਵੋਲਟੇਜ ਇੰਟਰਲਾਕ ਦੀ ਪ੍ਰਭਾਵੀ ਸੰਪਰਕ ਲੰਬਾਈ ਦੇ ਵਿਚਕਾਰ ਅੰਤਰ ਦੇ ਆਕਾਰ ਨਾਲ ਸੰਬੰਧਿਤ ਹੁੰਦਾ ਹੈ। ਟਰਮੀਨਲ ਅਤੇ ਪਾਵਰ ਟਰਮੀਨਲ ਅਤੇ ਡਿਸਕਨੈਕਸ਼ਨ ਦੀ ਗਤੀ। ਆਮ ਤੌਰ 'ਤੇ, ਇੰਟਰਲੌਕਿੰਗ ਟਰਮੀਨਲ ਸਰਕਟ ਲਈ ਸਿਸਟਮ ਦਾ ਪ੍ਰਤੀਕਿਰਿਆ ਸਮਾਂ 10 ~ ਅਤੇ 100ms ਦੇ ਵਿਚਕਾਰ ਹੁੰਦਾ ਹੈ ਜਦੋਂ ਕਨੈਕਸ਼ਨ ਸਿਸਟਮ ਨੂੰ ਵੱਖ ਕਰਨ (ਅਨਪਲੱਗਿੰਗ) ਸਮਾਂ ਸਿਸਟਮ ਪ੍ਰਤੀਕਿਰਿਆ ਸਮੇਂ ਤੋਂ ਘੱਟ ਹੁੰਦਾ ਹੈ, ਤਾਂ ਇਲੈਕਟ੍ਰੀਫਾਈਡ ਪਲੱਗਿੰਗ ਅਤੇ ਅਨਪਲੱਗਿੰਗ ਦਾ ਸੁਰੱਖਿਆ ਜੋਖਮ ਹੁੰਦਾ ਹੈ, ਅਤੇ ਸੈਕੰਡਰੀ ਅਨਲੌਕਿੰਗ ਇਸ ਡਿਸਕਨੈਕਸ਼ਨ ਸਮੇਂ ਦੀ ਸਮੱਸਿਆ ਨੂੰ ਹੱਲ ਕਰਨ ਲਈ ਤਿਆਰ ਕੀਤੀ ਗਈ ਹੈ, ਆਮ ਤੌਰ 'ਤੇ, ਸੈਕੰਡਰੀ ਅਨਲੌਕਿੰਗ ਇਸ ਡਿਸਕਨੈਕਸ਼ਨ ਸਮੇਂ ਨੂੰ ਪ੍ਰਭਾਵਸ਼ਾਲੀ ਢੰਗ ਨਾਲ ਕੰਟਰੋਲ ਕਰ ਸਕਦੀ ਹੈ 1s ਤੋਂ ਵੱਧ, ਓਪਰੇਸ਼ਨ ਦੀ ਸੁਰੱਖਿਆ ਨੂੰ ਯਕੀਨੀ ਬਣਾਉਣ ਲਈ.

ਇੰਟਰਲਾਕ ਸਿਗਨਲ ਦਾ ਜਾਰੀ ਕਰਨਾ, ਰਿਸੈਪਸ਼ਨ ਅਤੇ ਨਿਰਧਾਰਨ ਇਹ ਸਭ ਬੈਟਰੀ ਮੈਨੇਜਰ (ਜਾਂ VCU) ਦੁਆਰਾ ਮਹਿਸੂਸ ਕੀਤੇ ਜਾਂਦੇ ਹਨ। ਜੇਕਰ ਕੋਈ ਉੱਚ-ਵੋਲਟੇਜ ਇੰਟਰਲਾਕ ਨੁਕਸ ਹੈ, ਤਾਂ ਵਾਹਨ ਨੂੰ ਉੱਚ-ਵੋਲਟੇਜ ਪਾਵਰ 'ਤੇ ਜਾਣ ਦੀ ਇਜਾਜ਼ਤ ਨਹੀਂ ਹੈ, ਅਤੇ ਵੱਖ-ਵੱਖ ਕਾਰ ਮਾਡਲਾਂ ਦੇ ਇੰਟਰਲਾਕ ਸਰਕਟਾਂ ਵਿੱਚ ਕੁਝ ਅੰਤਰ ਹਨ (ਇੰਟਲਾਕ ਪਿੰਨਾਂ ਵਿੱਚ ਅੰਤਰ ਅਤੇ ਇੰਟਰਲਾਕ ਵਿੱਚ ਸ਼ਾਮਲ ਉੱਚ-ਵੋਲਟੇਜ ਹਿੱਸੇ ਸਮੇਤ ).

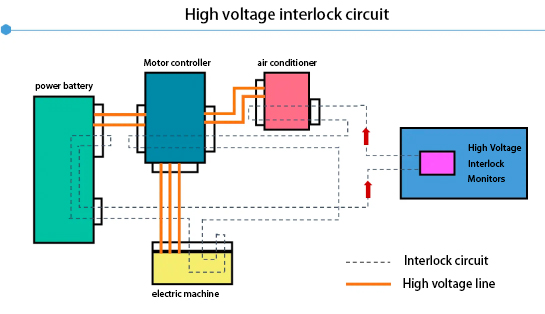

ਉਪਰੋਕਤ ਚਿੱਤਰ ਇੱਕ ਹਾਰਡਵਾਇਰਡ ਇੰਟਰਲਾਕ ਦਿਖਾਉਂਦਾ ਹੈ, ਇੱਕ ਇੰਟਰਲਾਕ ਸਰਕਟ ਬਣਾਉਣ ਲਈ ਲੜੀ ਵਿੱਚ ਹਰੇਕ ਉੱਚ-ਵੋਲਟੇਜ ਕੰਪੋਨੈਂਟ ਕਨੈਕਟਰ ਤੋਂ ਫੀਡਬੈਕ ਸਿਗਨਲਾਂ ਨੂੰ ਜੋੜਨ ਲਈ ਇੱਕ ਹਾਰਡਵਾਇਰ ਦੀ ਵਰਤੋਂ ਕਰਦੇ ਹੋਏ, ਜਦੋਂ ਸਰਕਟ ਵਿੱਚ ਇੱਕ ਉੱਚ-ਵੋਲਟੇਜ ਕੰਪੋਨੈਂਟ ਇੰਟਰਲਾਕ ਕਰਨ ਵਿੱਚ ਅਸਫਲ ਹੋ ਜਾਂਦਾ ਹੈ, ਤਾਂ ਇੰਟਰਲਾਕ ਨਿਗਰਾਨੀ ਉਪਕਰਣ ਤੁਰੰਤ VCU ਨੂੰ ਰਿਪੋਰਟ ਕਰੋ, ਜੋ ਸੰਬੰਧਿਤ ਪਾਵਰ ਡਾਊਨ ਰਣਨੀਤੀ ਨੂੰ ਲਾਗੂ ਕਰੇਗਾ। ਹਾਲਾਂਕਿ, ਇਹ ਨੋਟ ਕੀਤਾ ਜਾਣਾ ਚਾਹੀਦਾ ਹੈ ਕਿ ਅਸੀਂ ਇੱਕ ਤੇਜ਼ ਰਫ਼ਤਾਰ ਕਾਰ ਨੂੰ ਅਚਾਨਕ ਪਾਵਰ ਗੁਆਉਣ ਨਹੀਂ ਦੇ ਸਕਦੇ ਹਾਂ, ਇਸ ਲਈ ਪਾਵਰ-ਡਾਊਨ ਰਣਨੀਤੀ ਨੂੰ ਲਾਗੂ ਕਰਨ ਵਿੱਚ ਕਾਰ ਦੀ ਗਤੀ ਨੂੰ ਧਿਆਨ ਵਿੱਚ ਰੱਖਿਆ ਜਾਣਾ ਚਾਹੀਦਾ ਹੈ, ਇਸਲਈ ਹਾਰਡ-ਤਾਰ ਵਾਲੇ ਇੰਟਰਲਾਕ ਹੋਣੇ ਚਾਹੀਦੇ ਹਨ। ਜਦੋਂ ਰਣਨੀਤੀ ਤਿਆਰ ਕੀਤੀ ਜਾਂਦੀ ਹੈ ਤਾਂ ਗ੍ਰੇਡ ਕੀਤਾ ਜਾਂਦਾ ਹੈ।

ਉਦਾਹਰਨ ਲਈ, BMS, RESS (ਬੈਟਰੀ ਸਿਸਟਮ), ਅਤੇ OBC ਨੂੰ ਲੈਵਲ 1, MCU ਅਤੇ MOTOR (ਇਲੈਕਟ੍ਰਿਕ ਮੋਟਰ) ਨੂੰ ਲੈਵਲ 2, ਅਤੇ EACP (ਇਲੈਕਟ੍ਰਿਕ ਏਅਰ ਕੰਡੀਸ਼ਨਿੰਗ ਕੰਪ੍ਰੈਸ਼ਰ), PTC, ਅਤੇ DC/DC ਨੂੰ ਲੈਵਲ 3 ਦੇ ਰੂਪ ਵਿੱਚ ਸ਼੍ਰੇਣੀਬੱਧ ਕੀਤਾ ਗਿਆ ਹੈ।

ਵੱਖ-ਵੱਖ ਇੰਟਰਲੌਕਿੰਗ ਪੱਧਰਾਂ ਲਈ ਵੱਖ-ਵੱਖ HVIL ਰਣਨੀਤੀਆਂ ਅਪਣਾਈਆਂ ਜਾਂਦੀਆਂ ਹਨ।

ਕਿਉਂਕਿ ਉੱਚ-ਵੋਲਟੇਜ ਦੇ ਹਿੱਸੇ ਪੂਰੇ ਵਾਹਨ ਵਿੱਚ ਵੰਡੇ ਜਾਂਦੇ ਹਨ, ਇਸ ਨਾਲ ਇੰਟਰਲਾਕ ਹਾਰਡਵਾਇਰ ਦੀ ਲੰਬਾਈ ਬਹੁਤ ਲੰਬੀ ਹੁੰਦੀ ਹੈ, ਨਤੀਜੇ ਵਜੋਂ ਗੁੰਝਲਦਾਰ ਤਾਰਾਂ ਅਤੇ ਘੱਟ-ਵੋਲਟੇਜ ਵਾਇਰਿੰਗ ਹਾਰਨੇਸ ਦੀ ਲਾਗਤ ਵਧ ਜਾਂਦੀ ਹੈ। ਹਾਲਾਂਕਿ, ਹਾਰਡਵਾਇਰ ਇੰਟਰਲੌਕਿੰਗ ਵਿਧੀ ਡਿਜ਼ਾਈਨ ਵਿੱਚ ਲਚਕਦਾਰ, ਤਰਕ ਵਿੱਚ ਸਰਲ, ਬਹੁਤ ਅਨੁਭਵੀ, ਅਤੇ ਵਿਕਾਸ ਲਈ ਅਨੁਕੂਲ ਹੈ।

ਪੋਸਟ ਟਾਈਮ: ਜਨਵਰੀ-26-2024